(相关资料图)

(相关资料图)

主芯片需要发送数据时,需要先发送DE/RE为高再发送数据信号D,但是由于RS485芯片原来处于接收模式,突然收到主芯片命令需要切换到发送模式,由于芯片内部的逻辑内部固有的延迟,切换需要时间。以TI的TI-SN65LBC184为例,见下图,图中意思是,将芯片的TX固定为3V,然后在DE、RE引脚上输入一个高电平,当输入上升50%后为基线,测量出输出A总线上电平到2.3V需要的时间,这个时间tPZH就是使能延迟。该芯片数值为3.5uS。换个说法就是,芯片从接收模式,切换到发送模式,需要经过3.5uS才能有驱动能力输出。如果换向后总线马上送出数据而不延迟,有3.5uS时间总线AB是没有驱动能力的,还是处于高阻状态,串口协议起始标志是TX由高到低跳变,如果不考虑改值,将会损失该占空比。

检察官担任法治副校长有了“指挥棒”

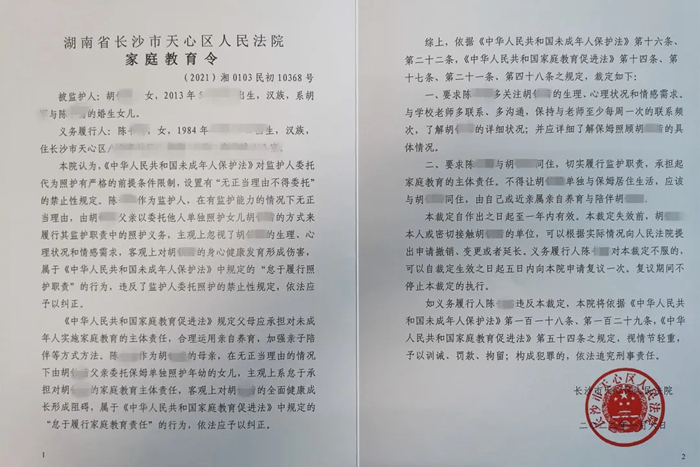

检察官担任法治副校长有了“指挥棒” 全国首份《家庭教育令》来了!督促家长“依法带娃”

全国首份《家庭教育令》来了!督促家长“依法带娃” 俄军装甲车辆将具备隐身能力

俄军装甲车辆将具备隐身能力